Breadcrumb

Hardware Speech Encryption Using a Chaotic Generator, Dynamic Shift and Bit Permutation

This paper proposes a speech encryption and decryption system, its hardware architecture design and FPGA implementation. The system utilizes Nosé Hoover chaotic generator and/or dynamic shift and bit permutation. The effect of different blocks in the proposed encryption scheme is studied and the security of the system is validated through perceptual and statistical tests. The complete encryption scheme is simulated using Xilinx ISE 14.5 and realized on FPGA Xilinx Kintex 7, presenting the experimental results on the oscilloscope. The efficiency is also validated through hardware resources

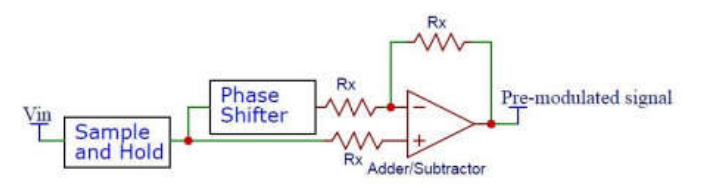

Memristor-based pulse width modulator circuit

This paper discusses the use of the memristor in one of the most important modulation techniques in communication field namely the pulse-width modulation. A fundamental two designs for memristor-based lead and trail PWM are discussed with mathematical analysis and PSPICE simulation results which show a great matching with the analytical formulation. Moreover, a third design which combine those two designs to generate a more accurate memristor-based center PWM is discussed with the appropriate analysis, numerical and PSPICE simulation results. The simulation results matches the theoretical

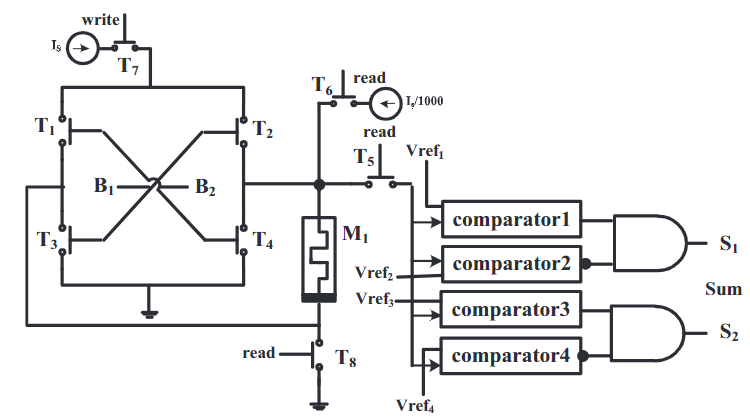

Memristor based N-bits redundant binary adder

This paper introduces a memristor based N-bits redundant binary adder architecture for canonic signed digit code CSDC as a step towards memristor based multilevel ALU. New possible solutions for multi-level logic designs can be established by utilizing the memristor dynamics as a basis in the circuit realization. The proposed memristor-based redundant binary adder circuit tries to achieve the theoretical advantages of the redundant binary system, and to eliminate the carry (borrow) propagation using signed digit representation. The advantage of carry elimination in the addition process is that

Memristor-based redundant binary adder

This paper introduces a memristor based redundant binary adder for canonic signed digit code, that coding eliminates the carry and provides a carry-free addition. The proposed binary adder circuit tries to achieve high addition speed that is independent on the length of the data using the accumulation property of a Nano-element called a memristor. The general block diagram of the proposed circuit is illustrated based on memristors and its operation has been validated using HP memristor model and simulated via different examples using PSPICE showing a great match. © 2014 IEEE.

Hermite polynomials in the fractional order domain suitable for special filters design

Due to the importance of its integer order counterpart in many mathematical and engineering fields, the fractional order Hermite polynomials are studied in this paper. A fractional variation of the well known Hermite differential equation is introduced based on Caputo fractional operator. The proposed equation is solved using fractional Taylor power series method and the convergence is verified using truncated series for different values of the parameters. The condition for fractional polynomial solution is obtained and the first four polynomials are scaled using an appropriate scaling factor

Memristor-CNTFET based Ternary Comparator unit

This paper proposes a new design for ternary logic comparator unit based on memristive threshold logic concept. To provide high-performance design, integrating memristor and Carbon Nano-Tube Field-Effect Transistor, CNTFET, is used. A comparison with other related work is presented to discuss performance aspects. It shows that performance has been improved by 75% compared with the other related work. Therefore, the proposed design is very promising to build high-performance full ternary ALU memristor-based unit. © 2018 IEEE.

Heating and Freezing Injury to Plant Tissues and Their Effect on Bioimpedance: Experimental Study

Electrochemical Impedance Spectroscopy (EIS) has been used as a technique for the assessment of food attributes. This paper discusses the effect of injuries caused by heating and freezing treatments to plant's bioimpedance. Unlike other studies to these kinds of injuries, experiments are carried out on the whole fruit using non-invasive electrodes keeping the plant tissues unharmed. Moreover, one of the samples under test was chosen to be a ripening fruit to discuss how its bioimpedance behavior differ from non-ripening ones. The experimental results showed how the damage caused by freezing

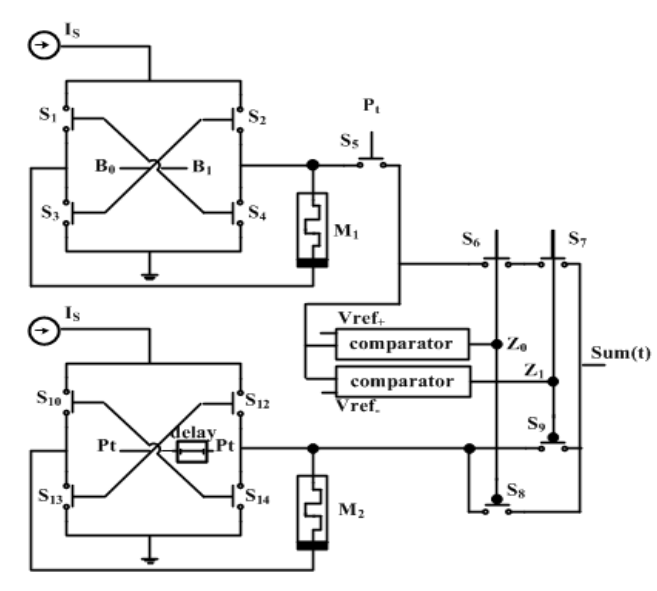

Memristor-based quinary half adder

This paper theorizes the possibilities of generalizing a memristor based ternary adder circuit, to a memristor based multi-valued logic adder. The proposition tries to achieve the theoretical advantages of processing different numbering systems, increasing the density, and decreasing the processing time, by utilizing the memristor properties and dynamics. This is done using a memristor cell based circuit structure. The memristor is quantized to more levels in order to accommodate more values of logic being processed. Quinary numbering system is used to demonstrate the generalization, then a

Synchronization and FPGA realization of fractional-order Izhikevich neuron model

This paper generalizes the Izhikevich neuron model in the fractional-order domain for better modeling of neuron dynamics. Accurate and computationally efficient numerical techniques such as non-standard finite difference (NSFD) scheme is used to solve the neuron system in the fractional-order domain for different cases. Neuron synchronization plays an important role in the process of information exchange among coupled neurons. The general formula for the synchronization of different Izhikevich neurons is proposed. Also, the synchronization of two and three neurons are studied at different

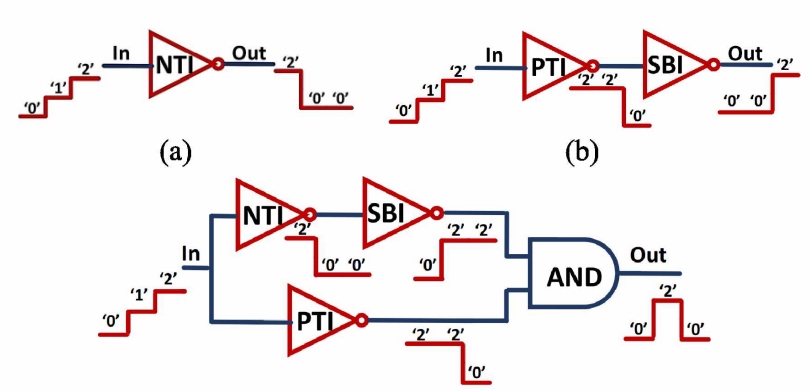

Ternary Functions Design Using Memristive Threshold Logic

Memristive threshold logic (MTL) concept is emerged in many circuits to enable high-performance systems in terms of power, energy, area, and delay. This paper proposes a systematic method for building two-bit ternary number functions based on the MTL concept. The proposed method is applied to build the basic ternary arithmetic operations. The implementation of two-bit adder and multiplier is presented in the unbalanced ternary number representation. The proposed designs are verified by using VTEAM memristor and Stanford CNTFET transistor models. Finally, a comparison between the proposed

Pagination

- Previous page ‹‹

- Page 3

- Next page ››