Comparative Study of CNTFET Implementations of 1-trit Multiplier

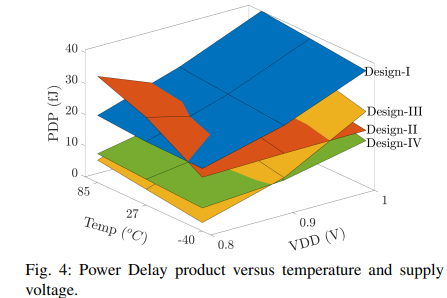

Ternary logic has become a promising alternative to traditional binary logic due to low power consumption and reduced circuits such as interconnects and chip areas. The efficiency of the multiplier circuit can be much better using a ternary logic system. Carbon nanotube field-effect transistor (CNTFET) is a promising technology as it achieves more advantages than MOSFET due to its low off-current features such as low power and high performance. This paper presents a comparative study of four implementations of a 1-trit multiplier based on CNTFET technology. The comparison is performed in terms of area, power, delay, and power delay product versus variation of supply voltage and temperature. The simulation results show that the proper PDP can be achieved using the transmission gate based multiplier. All the designs are implemented using the Virtual Source CNTFET (VS-CNTFET) Stanford model. © 2020 IEEE.